Состояние отечественных разработок в области высокопроизводительных вычислений

Микросхема сигнального процессора 1892ВМ2Я

Состав центрального процессора (CPU) во многом аналогичен центральному процессору микросхемы 1892ВМ3Т.

Архитектура ядра — совместимая с MIPS32, имеет 32-битные шины передачи адреса и данных, кэш команд объемом 16 Кбайт, внутреннюю оперативную память объемом 32 Кбайт, аппаратные блоки умножения и деления. Производительность составляет 80 млн оп./с.

Поддерживается архитектура привилегированных ресурсов в стиле ядра R4000: регистры Count/Compare для прерываний реального времени, отдельный вектор обработки исключений по прерываниям.

Программируемое устройство управления памятью: два режима работы — с TLB (Translation Look aside Buffer) и FM (Fixed Mapped), 16 строк в режиме TLB.

Для отладки используются интерфейс JTAG IEEE 1149.1, встроенные средства отладки программ.

Цифровой сигнальный процессор (DSP) микросхемы 1892ВМ2Я построен по "гарвардской" RISC-подобной архитектуре и преимущественно однотактным исполнением инструкций. Поддерживается 2SIMD (Single Instruction Multiple Data) организация потоков команд и данных. Имеет стандартный набор инструкций, процедуры обработки данных и пересылки совмещаются; трехступенчатый конвейер по выполнению 32-и 64-разрядных инструкций. Реализована аппаратная поддержка программных циклов. В состав сигнального ядра включена память программ PRAM объемом 16 Кбайт и двухпортовые памяти данных XRAM и YRAM объемом 128 и 32 Кбайт соответственно.

Расширены возможности по динамическому диапазону обрабатываемых данных, позволяющие обрабатывать данные в 8/16/32-разрядных форматах с фиксированной точкой либо в одном из форматов с плавающей точкой — 24Е8 (стандарт IEEE 754) или 32Е16 (расширенный формат). При этом обеспечивается возможность компромиссного выбора между точностью и производительностью. Реализованы аппаратные меры повышения точности и динамического диапазона (блочная плавающая точка; режим насыщения; инструкции преобразования форматов).

Пиковая производительность DSP:

- 480 млн оп./с 32-битных операций с плавающей точкой (IEEE 754);

- 2880 млн оп./с 8-битных операций с фиксированной точкой;

- 1280 млн оп./с 16-битных операций с фиксированной точкой;

- 640 млн оп./с 32-битных операций с фиксированной точкой. Порт внешней памяти (MPORT):

- шина данных — 64 разряда, шина адреса — 32 разряда;

- встроенный контроллер управления статической памятью типа SRAM, FLASH, ROM, а также синхронной динамической памятью типа SDRAM;

- программное конфигурирование типа памяти и объема ее сегмента, задание циклов ожидания, формирование сигналов выборки 4 сегментов памяти.

Обеспечивается обслуживание 4 внешних прерываний. SDRAM имеет режим энергосбережения.

Периферийные устройства:

- 12-канальный контроллер прямого доступа в память (DMA); 4 внешних запроса прямого доступа; специальные режимы синхронизации; поддержка 2-мерной и разрядно-инверсной адресации; режим передачи Flyby, подобный реализованному в ADSP-TS201: внешнее устройство — внешняя память;

- два порта обмена последовательным кодом (SPORT), совместимые с ADSP21160 (разработка фирмы ADI);

- четыре порта связи (LPORT), совместимые с ADSP21160; имеется режим работы в качестве портов ввода-вывода общего назначения (GPIO);

- универсальный асинхронный порт (UART) типа 16550;

- набор таймеров — 32-разрядный интервальный таймер (IT), 32-разрядный таймер реального времени (RTT), 32-разрядный сторожевой таймер (WDT).

Дополнительные возможности и особенности:

- узел фазовой автоподстройки частоты (PLL) c умножителем/делителем входной частоты;

- встроенные средства отладки программ (OnCD);

- порт JTAG в соответствии со стандартом IEEE 1149.1.

Рассеиваемая мощность, мВт, — около 1500 (максимальная); режимы энергосбережения: 700 — при неработающем DSP-ядре (режим Stop); 80 — при программном уменьшении тактовой частоты в 16 раз; 30 — при программном отключении тактовой частоты (включение тактовой частоты осуществляется по внешним прерываниям);

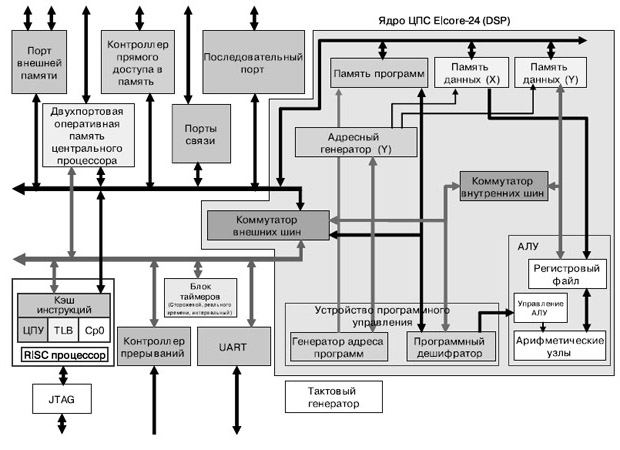

CPU-ядро является ведущим в двухпроцессорной конфигурации микросхемы ( рис. 14.3) и выполняет основную программу. Для CPU-ядра обеспечен доступ к ресурсам DSP-ядра, являющегося ведомым по отношению к CPU-ядру: обмен данными CPU-ядра с ресурсами DSP-ядра выполняется по командам LOAD, STORE. Память DSP-ядра и его регистры для CPU-ядра 32-разрядные (словные), то есть состояние двух младших разрядов адреса игнорируется.

CPU-ядро управляет работой DSP-ядра, передавая ему задание (макрокоманду). Затем запускает DSP-ядро, переводя его из режима STOP в режим RUN. С другой стороны, DSP-ядро формирует следующие прерывания в CPU-ядро: программное; по переполнению стека; при выполнении команды STOP; при достижении адреса останова при исполнении программы до адреса останова или завершении требуемого числа шагов при пошаговом исполнении программы. Состав процессора:

Состав процессора:

CPU — центральный процессор на основе RISC-ядра;

CRAM — двухпортовая оперативная память центрального процес- сора;

DSP — сопроцессор цифровой обработки сигналов с фиксирован- ной точкой;

DMA — контроллер прямого доступа в память;

SPORT — последовательный порт;

UART — универсальный асинхронный порт;

ICACHE — кэш программ центрального процессора;

RTT — таймер реального времени;

A[31:0] — шина адреса порта внешней памяти;

D[63:0] — шина данных порта внешней памяти;

OnCD — встроенные средства отладки программ;

XRAM, YRAM — памяти данных DSP;

EDBS — коммутатор внешних шин;

IDBS — коммутатор внутренних шин;

PCU — устройство программного управления;

PAG — генератор адреса программ;

ALU — арифметическое устройство;

XDB0 — XDB3, GDB, PDB — шина данных DSP;