|

приветствую создателей курса и благодарю за доступ к информации! понимаю, что это уже никто не исправит, но, возможно, будут следующие версии и было бы неплохо дать расшифровку сокращений имен регистров итд, дабы закрепить понимание их роли в общем процессе. |

Процессоры цифровой обработки сигналов

Цифровой сигнальный процессор ADSP BF561

В ряде задач, например, в задачах обработки видеоизображений с высоким разрешением, мощности одного, даже высокопроизводительного процессора оказывается недостаточно. Решение этой проблемы идет по двум направлениям.

Во-первых, это создание мультипроцессорных систем. В некоторых DSP-семействах для наращивания производительности предусмотрены специальные аппаратные средства, облегчающие создание мультипроцессорных систем с параллельной обработкой данных.

Во-вторых, это разработка многоядерных цифровых сигнальных процессоров, аналогично такому же направлению в развитии архитектуры универсальных МП. Рассмотрим второй подход на примере цифрового сигнального процессора ADSP BF561 фирмы Analog Devices.

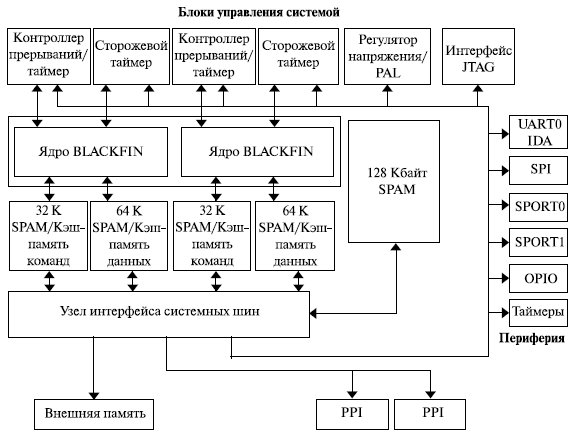

Основные функциональные блоки процессора показаны на рис. 16.6.

Основу процессора составляют два вычислительных ядра BLACKFIN, каждое из которых имеет свой набор ресурсов, включающий вычислительный блок, блок управления и набор регистров.

Основу вычислительного блока составляют два 16-разрядных MACустройства. Так как процессор работает на частоте 600 МГц, это обеспечивает выполнение MAC-операций с эквивалентной частотой 2,4 ГГц (по 2 MAC-устройства в каждом из двух ядер).

Помимо этого в вычислительный блок каждого из ядер входят следующие устройства:

- два 40-разрядных АЛУ для выполнения обычных арифметических и логических операций над 16- и 32-разрядными данными;

- 40-разрядное устройство сдвига, выполняющее помимо собственно сдвигов различных типов также нормализацию и извлечение экспоненты, обработку отдельных бит или наборов бит;

- четыре 8-разрядных видео-АЛУ, которые поддерживают некоторые операции над 8-разрядными данными, характерные для задач обработки видеоизображений;

- блок регистров общего назначения, включающий восемь 32-разрядных регистров, каждый из которых в зависимости от конкретной операции может рассматриваться как одно 32-разрядное слово или как два 16-разрядных.

Каждое ядро процессора имеет собственную память емкостью 100 Кбайт, доступную только ему и работающую на частоте ядра: 32 Кбайт памяти команд, из которых 16 Кбайт могут быть сконфигурированы как кэш команд, 64 Кбайт памяти данных, из которых 32 Кбайт могут быть сконфигурированы как кэш данных, и 4 Кбайта специального ОЗУ для сохранения контекста (scratchpad).

На кристалле также имеется менее быстродействующая (работающая на половине частоты ядра) память второго уровня объемом 128 Кбайт, доступная обоим ядрам. В ней могут храниться как команды, так и данные.

К процессору через 32-разрядную шину данных может быть подключено до четырех банков внешней памяти емкостью от 16 до 128 Мбайт каждый с общей емкостью до 512 Мбайт.

Отдельного адресного пространства ввода/вывода в процессоре нет, и адресация ко всем ресурсам проводится посредством единого 32-разрядного адреса.

Процессор имеет 10-уровневый конвейер команд.

Процессор ADSP BF561 имеет очень богатый набор интегрированных периферийных узлов, часть из которых входит в состав каждого из ядер, а другие являются общими ресурсами процессора. Сюда относятся:

- 14 32-разрядных таймеров, 12 из которых являются общими и могут также программироваться как ШИМ-генераторы, а еще два используются каждым из ядер;

- два сторожевых таймера (по одному в каждом из ядер);

- 4-канальный внутренний контроллер ПДП для ускорения обмена между блоками памяти внутри процессора;

- 32- и 16-разрядный контроллеры ПДП; каждый из этих контроллеров имеет по 12 каналов для пересылок между внутренней памятью процессора и периферией и по 4 канала для пересылок между внутренней и внешней памятью;

- контроллер прерываний системы, который преобразует все прерывания от периферийных узлов, контроллеров ПДП и внешние прерывания (всего 61 источник) в прерывания ядра общего назначения;

- по одному контроллеру прерываний в каждом из ядер, которые поддерживают 9 прерываний общего назначения и выделенные прерывания: сброса, эмуляции, немаскируемое прерывание, прерывания от таймеров и т. д.;

- два 16-разрядных параллельных порта PPI, которые позволяют без использования дополнительной логики подключать к процессору многие стандартные АЦП, ЦАП, видеокодеры и декодеры;

- 48 программируемых портов ввода-вывода общего назначения (GPIO);

- набор стандартных последовательных интерфейсов - SPI, SPORT и UART (с поддержкой IrDA) и т. д.

Процессор поддерживает режимы прямой адресации, косвенной адресации с пред- и постинкрементом и специфические для задач цифровой обработки сигналов режимы циклической адресации и адресации с реверсированием бит адреса.

Система команд процессора, аналогично RISC-микропроцессорам, имеет структуру, ориентированную на регистры и поддержку языков высокого уровня.

Краткие итоги. В лекции рассмотрен особый класс микропроцессорных БИС - цифровые сигнальные процессоры. Приведены примеры цифровой обработки сигналов и используемого при этом дискретного преобразования Фурье. Выделены особенности ЦСП, вытекающие из области их применения и существенно влияющие на их архитектуру.

Рассмотрена архитектура сигнальных микропроцессоров TMS320F2833x фирмы Texas INsTRuments и ADSP BF561 фирмы Analog Devices, имеющие в настоящее время наилучшие характеристики в этом классе микропроцессоров.