Сегментная организация памяти

Пример сегментной организации памяти

В примере программа использует пять сегментов с номерами от 0 до 4: сегмент 0 – подпрограмма, сегмент 1 – стандартные подпрограммы ( sqrt и др.), сегмент 2 – основная программа, сегмент 3 – стек, сегмент 4 – таблица символов. Показано размещение сегментов в памяти.

Пример использования разделяемых сегментов

В примере два процесса используют общий сегмент – код редактора, который имеет в таблицах сегментов обоих процессов один и тот же номер – 0. Кроме того, каждый из процессов имеет собственный сегмент данных с номером 1, однако эти сегменты, естественно, у обоих процессов разные.

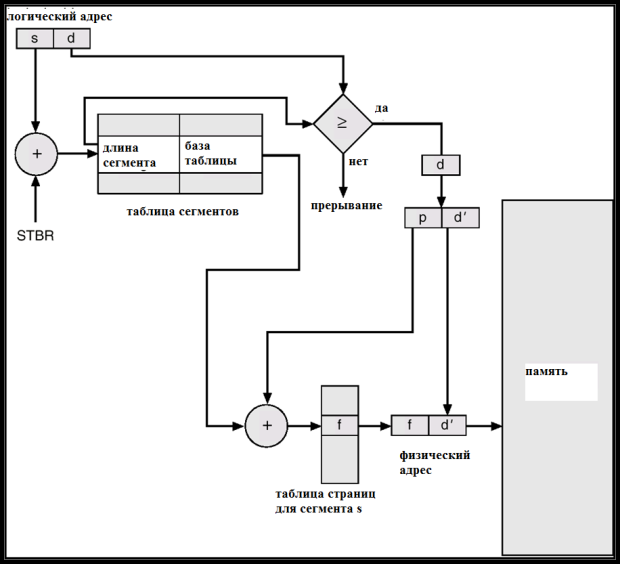

Сегментно-страничная организация памяти в системах MULTICS и "Эльбрус"

Сегментное распределение памяти, как видно из предыдущих пунктов, имеет свои неоспоримые преимущества. Однако, к сожалению, проблема внешней фрагментации при чисто сегментной организации памяти весьма серьезна.

Поэтому в системе MULTICS проблемы внешней фрагментации и длительного времени поиска решены путем страничной организации памяти для сегментов. Данное решение отличается от чисто сегментной организации тем, что элемент таблицы сегментов содержит не базовый адрес сегмента, а базовый адрес таблицы страниц для данного сегмента.

В системе "Эльбрус" данные проблемы решены по-другому: в системе используется страничная организация для математической (виртуальной, логической) памяти и сегментная организация – для физической памяти. Математическая память (т.е. образ памяти на диске) распределяется с точностью до страницы,а физическая – с точностью до слова. Кроме того, как уже отмечалось, для адресации в системе "Эльбрус" используются дескрипторы массивов, содержащие начальный адрес, длину и признаки защиты массива.

Схема трансляции адресов в MULTICS приведена на рис. 17.5.

Логический адрес (s, d) используется следующим образом. Номер сегмента s складывается с содержимым регистра STBR, после чего происходит обращение по полученному адресу в таблицу сегментов. Смещение d сравнивается с длиной сегмента; если оно больше или равно длине сегмента,то прерывание. Из элемента таблицы сегментов извлекается адрес базы таблицы страниц данного сегмента, который складывается со старшими разрядами смещения ( p ). Младшие разряды смещения используются как смещение внутри страницы, адрес которой извлекается из таблицы страниц данного сегмента.

Нельзя не отметить, что данная схема, на наш взгляд, несколько усложнена. Система MULTICS, в которой этот и многие другие механизмы доведены, казалось бы, до совершенства, вызвала противоположную тенденцию в развитии ОС – к упрощению. Как мы уже говорили, даже название следующей системы – UNIX – выбрано как противоположность MULTICS, что говорит о многом. Таковы тенденции развития во многих областях, в том числе и в операционных системах.

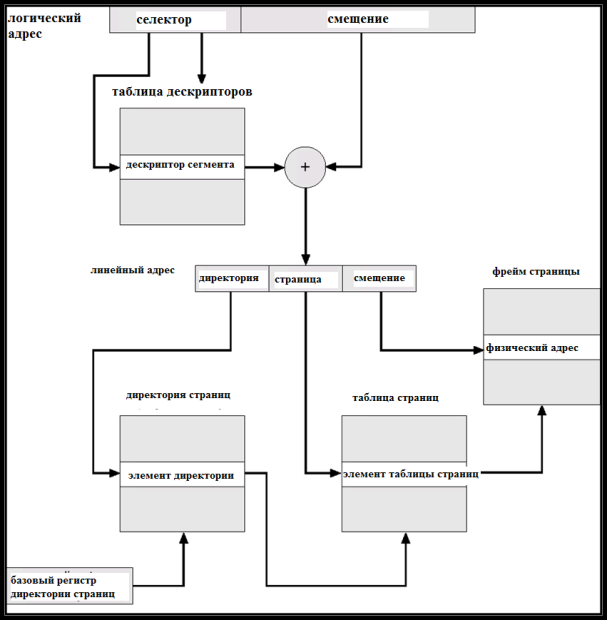

Сегментно-страничная организация памяти в системе Intel 386

В более современных системах, чем MULTICS, также используется сегментно-страничная организация. Например, в системе Intel 386 используется сегментно-страничная организация памяти с двухуровневой схемой страничной организации (см. рис. 17.6).

Ключевые термины

Базовый регистр таблицы сегментов - segment-table base register (STBR) – регистр, содержащий адрес таблицы сегментов в памяти.

Логический адрес при сегментной организации памяти - пара:

<segment-number, offset>,где segment-number – номер сегмента, offset – смещение в сегменте.

Признаки защиты – информация для защиты сегмента в элементе таблицы сегментов: validation-бит (признак корректности номера сегмента для процесса), биты защиты от записи, от чтения и от исполнения.

Разделяемые (общие) сегменты – сегменты, общие для нескольких процессов и имеющие одинаковые логические номера в их таблицах сегментов.

Регистр длины таблицы сегментов - segment-table length register (STLR) – регистр, содержащий число сегментов, используемое программой.

Сегмент – логическая единица распределения памяти, предназначенная для размещения в памяти одного модуля программного кода или данных.

Сегментная организация памяти (segmentation) - схема распределения памяти в виде сегментов переменной длины, соответствующая пользовательской трактовке распределения памяти, т.е. логической структуре программ и данных.

Сегментно-страничная организация памяти – модификация сегментной организации памяти для борьбы с фрагментацией, основанная на страничной организации каждого сегмента.

Таблица сегментов – системная таблица для отображения логических адресов в физические при сегментной организации памяти. Каждый ее элемент содержит начальный адрес сегмента в физической памяти, длину сегмента и признаки защиты.

Краткие итоги

Сегментная организация памяти – страгетия распределения памяти сегментами переменной длины, каждый из которых выполняет определенную логическую функцию в программе как модуль программы или данных – стек, массив, подпрограмма и т.д.

При сегментной организации логический адрес имеет вид: (номер сегмента, смещение внутри сегмента). Организуется системная таблица сегментов, каждый элемент которой содержит базовый адрес сегмента, его длину и признаки защиты – validation-бит, определяющий корректность номера сегмента, биты защиты от записи, чтения и исполнения. Базовый регистр таблицы сегментов содержит начальный адрес таблицы сегментов, регистр длины таблицы сегментов содержит ее длину.

Перемещение при сегментной организации осуществляется динамически, во время выполнения программы.

Возможен общий доступ нескольких процессов к одному и тому же сегменту с одним логическим номером (разделяемые сегменты).

Стратегии распределения памяти при сегментной организации – методы первого подходящего и наиболее подходящего. Возможна внешняя фрагментация.

При адресации по логическому адресу для сегментной организации смещение внутри сегмента сравнивается с длиной сегмента из элемента таблицы сетментов. В случае превышения – прерывание.

Для борьбы с фрагментацией в некоторых системах (MULTICS, "Эльбрус|", Intel 386) применяется смешанная, сегментно-страничная организация памяти, при которой для каждого сегмента организуется собственная таблица страниц.

Набор для практики

Вопросы

- Что такое сегментная организация памяти?

- Что такое сегмент?

- Приведите примеры модулей кода и данных, память для которых распределяется в виде отдельных сегментов.

- Какую структуру имеет логический адрес при сегментной организации памяти?

- Что такое таблица сегментов?

- Какая информация хранится в элементе таблицы сегментов?

- Что такое регистр базы таблицы сегментов?

- Что такое регистр длины таблицы сегментов?

- На какой фазе (во время загрузки или исполнения) осуществляется перемещение при сегментной организации?

- Какие стратегии распределения памяти применяются при сегментной организации?

- Какие признаки защиты хранятся в элементе таблицы сегментов?

- Какое условие для номера сегмента проверяется при адресации?

- Что такое сегментно-страничная организация и для какой цели она используется?

Упражнения

- Реализуйте представление логического адреса при сегментной организации памяти, модель таблицы сегментов и схемы адресации.

- Реализуйте представление логического адреса при сегментно-страничной организации памяти, модель таблицы сегментов и схемы адресации.

Темы для курсовых работ, рефератов, эссе

- Обзор методов сегментной организации памяти в компьютерных системах (реферат).

- Обзор методов сегментно-страничной организации памяти в компьютерных системах (реферат).

- Реализация представления логического адреса при сегментной организации памяти, модели таблицы сегментов и схемы адресации (курсовая работа).

- Реализация представления логического адреса при сегментно-страничной организации памяти, модели таблицы сегментов и схемы адресации (курсовая работа).