|

Добрый день можно поинтересоваться где брать литературу предложенную в курсе ?Большинство книг я не могу найти в известных источниках |

Неконстантные неисправности

10.3 Неисправности типа "задержка"

В современных цифровых системах возможны ситуации, когда схема структурно и логически корректна, но время распространения сигналов по некоторым ее путям превышает допустимое для правильного функционирования значение. В таких случаях говорят о наличии неисправности типа "задержка" (распространения сигналов). Такие неисправности не могут быть обнаружены на низкой частоте работы схемы. Целью тестирования неисправностей "задержка" является определение правильного функционирования схемы на высоких тактовых рабочих частотах. При этом выявляется, содержит ли схема пути распространения сигналов, которые являются слишком медленными или быстрыми при смене входных наборов. Для этих целей используются две основные модели:

- задержка вентиля,

- задержка пути.

Первая модель предполагает, что задержка обусловлена в неисправным логическим элементом. Следует отметить, что время переключения элемента, может зависеть от направления изменения сигнала - его подъема или спада. Это является недостатком данной модели, поскольку не позволяет в задержке одного элемента учесть задержки других элементов пути. Очевидно, здесь также полностью игнорируются задержки соединений между элементами.

Вторая модель принимает во внимание общую задержку распространения сигнала от внешнего входа до внешнего выхода схемы. Хотя данная модель требует рассмотрения слишком многих возможных путей в схеме, она более реалистична, особенно для современных технологий, где задержки распространения сигналов имеют место прежде всего за счет линий соединений. Как правило, тестирование задержек производится путем подачи на схему пары входных наборов на желаемой скорости и наблюдении для каждого изменившегося выхода скорости его переключения. Подробнее вопросы моделирования и тестирования будут рассмотрены в "Моделирование неисправностей задержек распространения сигналов" .

10.4 Временные неисправности

При данных неисправностях происходит временное появление неправильных сигналов в схеме. Они встречаются в различных цифровых элементах, но чаще всего в микросхемах памяти и микропроцессоров. Среди этих неисправностей различают "кратковременные" (transient) "сбои" intermittent.

Кратковременные неисправности происходят, когда сигналы меняют свое значение вследствие, например, шумов. Такие неисправности тяжело обнаружить и исправить. Здесь важно минимизировать шумы и повысить помехозащищенность схемы. Данные неисправности могут быть вызваны, например, флуктуациями напряжения, метастабильностью триггеров или космическим излучением [10.2].

Сбои являются одной из причин отказов при эксплуатации компьютерных систем. Очень мало известно о спонтанных отказах, поскольку они плохо поддаются наблюдению. Среди них можно выделить кодозависимые неисправности, которые встречаются в микросхемах памяти и микропроцессорах. Для этих неисправностей разработаны соответствующие методы тестирования [10.2].

10.5 Функциональные неисправности переменных данных и управления

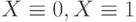

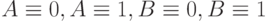

В настоящее время при тестировании сложных компьютерных (в частности микропроцессорных) систем широко применяются модели неисправностей на функциональном уровне. В простейшем случае модель константной неисправности распространяется на переменные операторов ЯРП. При этом подразумеваются постоянные значения отдельных переменных. Обычно различают неисправности "данных" и "управления" в зависимости от типа переменных, которые они фиксируют. Неисправности "данных", как правило, связывают с памятью или регистрами. Неисправности "управления" связаны с переменными, описывающими, например, условия выполнения некоторой операции. Рассмотрим для примера следующий оператор:

Здесь константная неисправность переменной  (

(

) является неисправностью "управления". Соответственно неисправности переменных

) является неисправностью "управления". Соответственно неисправности переменных  ,

,  (

( ) являются неисправностями "данных".

) являются неисправностями "данных".

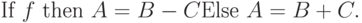

Иногда функционирование неисправного устройства описывается с помощью операторов ЯРП. При этом вводится специальная переменная неисправности  , которая является признаком присутствия неисправности. Покажем это на следующем примере [10.4]:

, которая является признаком присутствия неисправности. Покажем это на следующем примере [10.4]:

Из данного описания видно, что в неисправной схеме (  ) выполняется

) выполняется  , а в исправной -

, а в исправной -  . Отметим, что это достаточно универсальный метод моделирования неисправностей. Например, таким образом можно моделировать и неисправности типа "задержка":

. Отметим, что это достаточно универсальный метод моделирования неисправностей. Например, таким образом можно моделировать и неисправности типа "задержка":

Здесь показано, что в неисправной схеме задержка равна 40 единицам в отличие от исправной схемы, где задержка равна 10 единицам. Но этот подход требует явного описания поведения фрагмента неисправной схемы, что, конечно, ограничивает его применение.

10.6 Неисправности уровня ЯРП

В настоящее время новые технологии позволяют проектировать сложные цифровые системы (ЦС) на одном кристалле (System-on-Chip - SOC). При этом проектирование ЦС выполняется с помощью достаточно сложных языков высокого уровня описания аппаратуры (HDL), таких как VHDL, Verilog и SpecC [10.4]. Поэтому актуальной является проблема верификации и тестирования сложных ЦС, описанных с помощью этих языков.

На логическом уровне моделирования, где ЦС представляется в виде логической схемы, основной моделью физических дефектов являются константные неисправности, которые эквивалентны постоянным сигналам 0 или 1 на линиях схемы.В отличие от логического уровня моделей неисправностей, где обычно можно установить соответствие между физическим дефектом проводников в кремнии и соединениями в логической схеме, на поведенческом уровне, как правило, трудно установить соответствие между описанием ЦС на HDL и структурным описанием. Один оператор HDL может соответствовать сотням логических вентилей, соединенных между собой. Поэтому необходимо рассматривать функциональные модели неисправностей непосредственно на языковых конструкциях HDL. При этом качество (или адекватность) функциональных моделей неисправностей, как правило, проверяется с помощью логического моделирования ЦС, которое определяет полноту теста относительно одиночных константных неисправностей схемы, реализующей ЦС. Поэтому данный подход ориентирован скорее на достижение высокой полноты теста для константных неисправностей, а не обнаружение ошибок в языковых конструкциях HDL. Более того, при этом эффективность тестовой последовательности не может быть определена непосредственно на функциональном уровне. Поэтому в настоящее время для верификации и тестирования ЦС, описанных на HDL, применяются методы, заимствованные из тестирования программного обеспечения [10.5].

10.7 Перекрестные (crosstalk) неисправности

Вследствие технологического прогресса, который ведет к увеличению плотности на кристалле, росту числа пересечений проводящих слоев и повышению рабочей частоты, тестирования классических константных неисправностей в настоящее время явно недостаточно, поскольку необходимо анализировать физические дефекты, которые влияют на временные характеристики схемы. Особенно это характерно для глубокого субмикронного (deep submicron - DSM) проектирования. Увеличение числа транзисторов на кристалле ведет к тому, что большее количество элементов переключаются одновременно, что может уменьшить для них уровень напряжения и увеличить задержки распространения сигналов. При этом некоторые пересекающиеся линии, которые предполагались электрически изолированными, могут взаимодействовать друг с другом. Одно из подобных взаимодействий, вызванное паразитической емкостной связью между проводниками, называется "crosstalk"(перекрестная помеха), может привести к функциональным проблемам и ухудшить временные характеристики.

Обычно рассматриваются два основных типа перекрестных помех: 1) "crosstalk" индуцированные импульсы; 2)"crosstalk" индуцированные задержки. В первом случае быстро переключающаяся линия - "агрессор" (aggressor) может индуцировать короткий импульс на статической линии - "жертве" (victim). В зависимости от амплитуды и ширины эти импульсы могут оказывать существенное влияние на характеристики схемы.

Второй случай (индуцированные задержки) имеет место тогда, когда на линиях "агрессоре" и "жертве" происходят (почти) одновременные переходы сигналов. Если на обеих линиях переходы в одном направлении, то время перехода сокращается и, следовательно, уменьшается время задержки распространения сигналов. Этот эффект называется "перекрестным ускорением" ("crosstalk speedup"). Сильный "агрессор" может вызвать задержку распространения сигнала на линии-"жертве", которая имеет противоположное значение сигнала. Если на линиях "агрессоре" и "жертве" происходят переходы сигналов в противоположных направлениях, то время перехода увеличивается и имеет место эффект "перекрестного замедления" ("crosstalk slowdown"). Если вызванный шум на линии-"жертве" больше порогового напряжения или индуцированная задержка больше допустимой, то это может привести к логическим отказам или функциональным проблемам на соседних триггерах или выходах.

Нееисправности первого типа "crosstalk glitch" - индуцированные импульсы вызываются наводкой между близко расположенными проводниками, которые имеют несбалансированные значения драйвера и нагрузки [10.6].

Перекрестные неисправности вызываются паразитическими наводками между соседними проводящими линиями, которые имеют, в основном, емкостные составляющие, поскольку для информационных линий в схемах доминируют емкостные связи. На рис. 10.6 показана модель перекрестного (crosstalk) эффекта, где  и

и  представляют емкости между линиями и землей, и

представляют емкости между линиями и землей, и  - емкость между соседними линиями. Величина импульса зависит от отношения емкостей

- емкость между соседними линиями. Величина импульса зависит от отношения емкостей  и

и  к

к  .

.

Когда на "сильной" линии (агрессоре) происходит изменение сигнала, а на слабой линии (жертве) сохраняется постоянный сигнал, то вследствие емкостной связи на жертве может возникнуть кратковременный импульс (glitch), что показано на рис. 10.7 а). Если этот импульс запоминается в элементе памяти, то он далее распространяется по схеме, что может привести к ее неправильному функционированию. Условием возникновения индуцированного импульса является  ,

, и

и  , где

, где  и

и  означают управляющие соотношения для активной (агрессор) и пассивной (жертва) линии. Эти условия позволяют отбирать кандидатов в пары агрессор-жертва при наличии информации о подложке.

означают управляющие соотношения для активной (агрессор) и пассивной (жертва) линии. Эти условия позволяют отбирать кандидатов в пары агрессор-жертва при наличии информации о подложке.

Если имеют место переходы сигналов на линиях "агрессоре" и "жертве" в одном направлении, то, как показано на рис. 10.7 б) происходит ускорение сигнала - время перехода уменьшается. Если же переходы на линиях имеют противоположные направления, то наблюдается замедление сигнала - время перехода увеличивается, что представлено на рис. 10.7 в).

Ключевые термины:

Замыкание - имеет место в том случае, происходит соединение двух и более линий и образуется "проводная логика" в месте возникшей электрической связи.

Транзисторные неисправности - транзистор "постоянно замкнут" (stuck on - SON), транзистор "постоянно открыт" (stuck open).

Задержка - увеличение времени распространения сигналов.

Перекрестные неисправности - пересекающиеся линии, которые предполагались электрически изолированными взаимодействуют друг с другом и порождают индуцированные импульсы или задержки.

Краткие итоги

Рассмотрены не константные модели неисправностей, которые дают возможность моделировать физические дефекты, возникающие при современных технологиях.

В "Неконстантные неисправности" приведены замыкания, которые моделируют проводную логику путем ввода фиктивного логического элемента.

"Неконстантные неисправности" посвящен транзисторным неисправностям типа транзистор "постоянно открыт" и "постоянно закрыт".

В "Неконстантные неисправности" изложены неисправности "задержка распространения сигналов" двух типов:

- задержка элемента;

- задержка пути.

В "Неконстантные неисправности" рассмотрены кратковременные неисправности и сбои.

"Неконстантные неисправности" -6 посвящены неисправностям, которые представляются на функциональном уровне на языковых конструкциях языков описания аппаратуры. Например, ЯРП.

В "Неконстантные неисправности" изложены перекрестные неисправности двух основных типов:

- индуцированные импульсы;

- индуцированные задержки.

Вопросы и упражнения

- Когда имеют место замыкания?

- При какой технологии в случае замыкания ставится "проводное И"?

- При какой технологии в случае замыкания ставится "проводное ИЛИ"?

- Приведите основные модели транзисторных неисправностей.

- Что такое неисправность транзистор "постоянно открыт"?

- Что такое неисправность транзистор "постоянно закрыт"?

- Приведите пример транзисторной неисправности вентильного уровня.

- Приведите две основные модели неисправностей типа задержка.

- что такое временные неисправности?

- Как определяются функциональные неисправности?

- приведите пример неисправности уровня ЯРП.

- Чем обусловлены перекрестные неисправности?

- Приведите два основных типа перекрестных неисправностей.

- Когда может возникнуть индуцированный импульс?

- При каких условиях могут возникнуть индуцированные задержки?

- Чем отличаются условия ускорения и замедления сигналов?